Click me ♫

Click me ♫

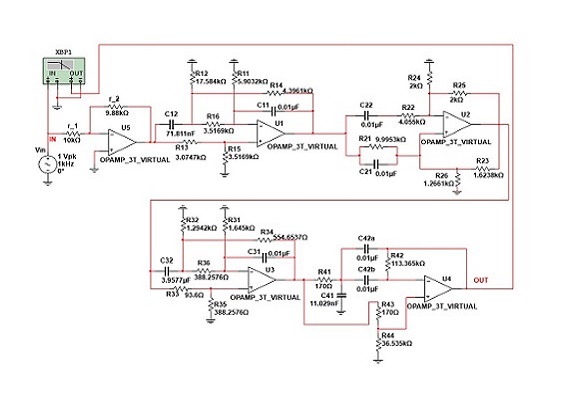

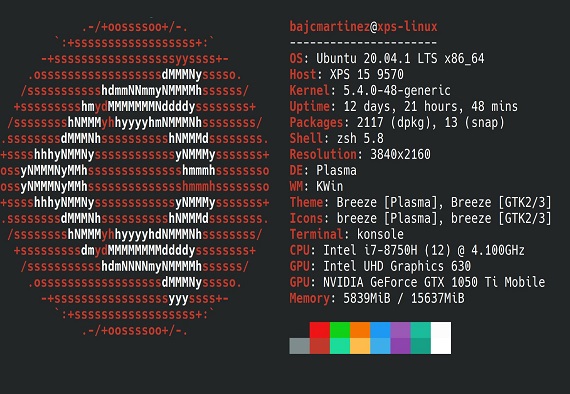

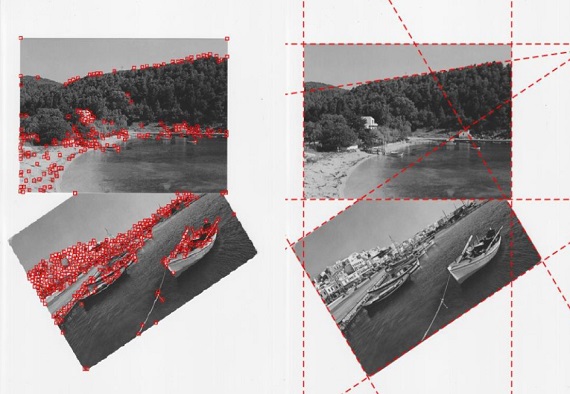

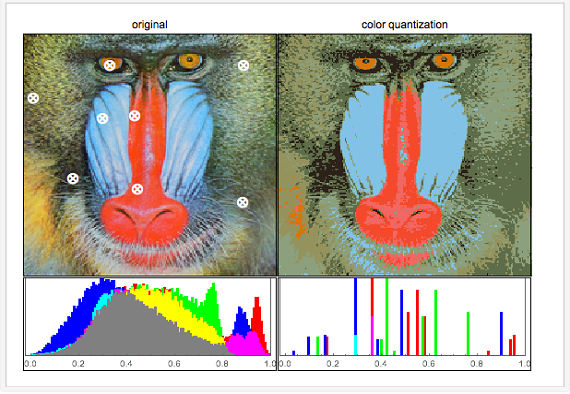

One area of interest for me is Artificial Intelligence and Signal Processing. I have experience in various areas of Machine Learning such as Computer Vision or Natural Language Processing. In particular, I am very interested in the applications of Artificial Iintelligence in Biomedical Engineering and Neuroscience.

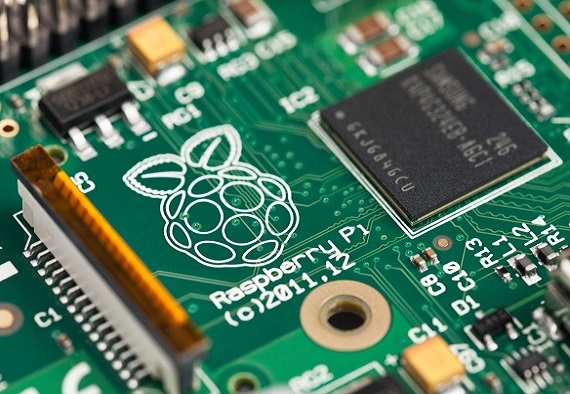

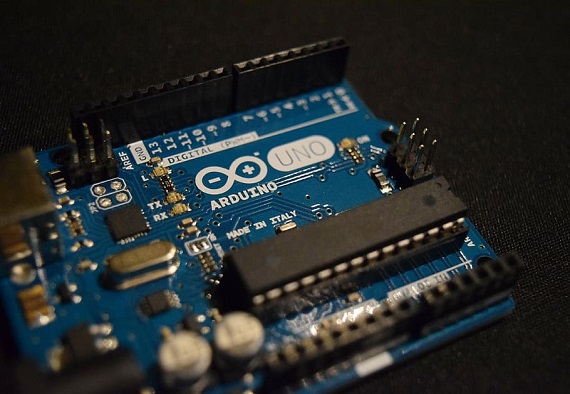

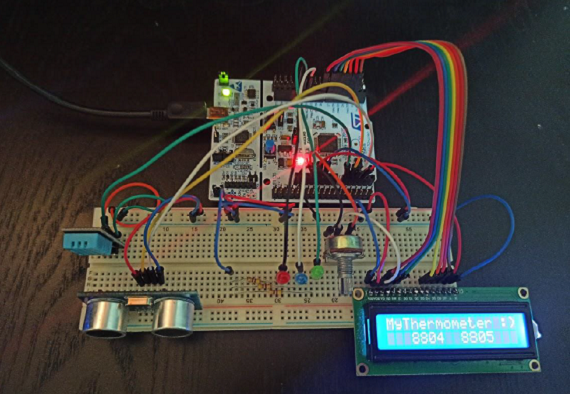

Another area of interest for me is the programming of Embedded Systems and Microcontrollers. Τhrough various academic projects I have become familiar with Arduino, Raspberry-Pi and STM32 boards. My programming mainly concerns the data acquisition from sensors and driving of peripherals. My working experience focused on testing of ASICs with FPGA based data acquisition systems.

Python

MATLAB

C / C++

Linux bash

Verilog/Vivado

Java

R

HTML / CSS / Javascript

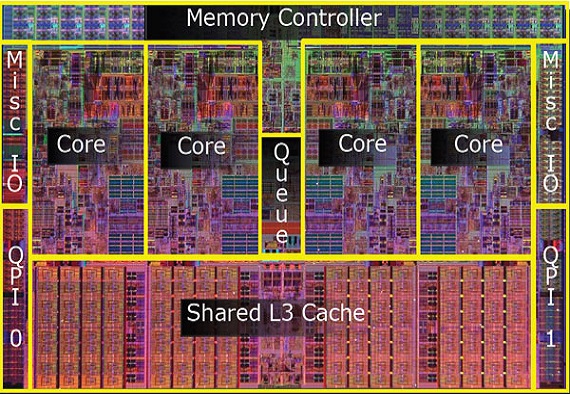

Member of the RD53 collaboration at EPE-ESE-ME section. Full time working on characterization of the final RD53 pixel ASICs for the upgrades of the ATLAS and CMS pixel detectors, using BDAQ53 data acquisition framework: • Software development for PC-FPGA communication: using Python to implement testing scenarios including command sending procedures using TCP socket programming, as well as readout data receiving and analyzing procedures. • Firmware development for Kintex-7 Xilinx FPGA: digital circuit design and simulation using Vivado and Verilog. • Lab instrumentation: Power supplies, Oscilloscope, Pulse Generators, Delay Generators, RF Attenuators and PCB soldering tools. • Development of Python drivers to communicate with instruments through TCP/IP, UDP (server-client architecture) and GPIB. • Investigation of Xilinx Aurora 64B/66B high-speed serial interface protocol for chip-to-chip and chip-to-DAQ communications. • Power measurements on oscilloscope under extreme injection cases of the sensor. Characterization of LDO and SLDO regulators. • Identification of a design bug in serial communication between chips due to clock jitter and transmission delay. Characterized by phase shifts between the clock of the sampler of primary’s deserializer and the data arrival time from the secondary chip. • Timing characterization of the distributed clocks to the pixel matrix. Injections of charge with custom made microprobes and serial capacitance to the preamplifier of the Analog Front Ends. (high-speed signal propagation, impedance matching requirements) • Using Git code versioning and CI/CD pipelines for testing. • Collaborating with a team, aligning testing with designers’ requirements, visualizing and presenting measurements at weekly meetings.

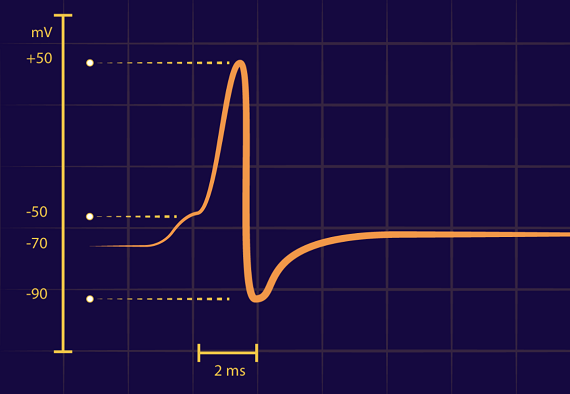

Full time working in the Computational section of a Neuroinformatics Lab, researching memory consolidation of mice. Using Python, MATLAB, Linux bash and Verilog: • Installation of Open Ephys FPGA boards, connected to tetrode electrodes (implants in mice) for electrophysiological data acquisition of extracellular neural activity. • Firmware modifications for the Opal Kelly XEM6310 FPGA in Verilog, which reads data from Intan’s RHD2132 headstages. • Electrophysiological data analysis: Analysis of Local Field Potential signals for the detection of high frequency events in cortex and hippocampus of rodents. • Machine Learning algorithms for the automatic classification of spiking activity: Classification of neuron types and computation of cells firing rates.

Full time work at the Information Technologies Institute on the development of a system for the assistance of obese and diabetic patients. Using Python to implement a novel dessert recognition system: Transfer Learning and fine-tuning of pretrained Convolutional Neural Networks.